# UNIT DESCRIPTION

## CONTENTS

| Paragr | aph   |          |                                   | Page |

|--------|-------|----------|-----------------------------------|------|

| 1.     | INTRO | DUCTIC   | DN                                | 1    |

|        | 1.1   | Gener    | al                                | 1    |

|        | 1.2   | Leadin   | ng Particulars                    | 1    |

|        |       | 1.2.1    | Mechanical                        | 1    |

|        |       | 1.2.2    | Power Supplies                    | 1    |

|        |       | 1.2.3    | Connections                       | 1    |

| 2.     | CIRC  | UIT DESC | CRIPTION                          | 3    |

|        | 2.1   | Microp   | processor                         | 3    |

|        |       | 2.1,1    | Microprocessor Registers          | 3    |

|        |       | 2.1.2    | Microprocessor Inputs and Outputs | 3    |

|        | 2.2   | Addres   | ss Select                         | 5    |

|        |       | 2.2.1    | RAM and VIA Selection             | 5    |

|        |       | 2.2.2    | ROM Selection                     | 7    |

|        | 2.3   | Syster   | n Clock                           | 7    |

|        | 2.4   | Wait C   | Sircuit                           | 8    |

|        | 2.5   | Ready    | / Circuit                         | 8    |

|        | 2.6   | -        | Write Control                     | 8    |

|        | 2.7   | Read (   | Only Memory                       | 9    |

|        | 2.8   | Rando    | om Access Memory                  | 9    |

|        | 2.9   | Data E   | Buffer                            | 9    |

|        | 2.10  | Versat   | ile Interface Adaptor             | 10   |

|        |       | 2.10.1   | Peripheral Control Register       | 12   |

|        |       | 2.10.2   | Auxiliary Control Register        | 13   |

|        |       | 2.10.3   | Shift Register                    | 13   |

|        |       | 2.10.4   | Interrupt Flag Register           | 14   |

|        |       | 2.10.5   | Interrupt Enable Register         | 14   |

|        |       | 2.10.6   | Timer 1                           | 14   |

|        |       | 2.10.7   | Timer 2                           | 14   |

|        | 2.11  | Power    | -on Reset                         | 14   |

| 3.     | SOFT  | WARE P   | ARAMETERS                         | 15   |

|        | 3.1   | 6502A    | Addressing Modes                  | 15   |

|        | 3.2   |          | instruction Set                   | 16   |

|        | 3.3   | Interru  | pts and Reset                     | 16   |

|        |       | 3.3.1    | Interrupt Request                 | 16   |

|        |       | 3.3.2    | Non-Maskable interrupt            | 16   |

|        |       | 3.3.3    | Reset                             | 16   |

|        | 3.4   | CPU N    | Nemory Addressing                 | 18   |

©1982 Acorn Computers Limited, 12 Fulbourn Road, Cherry Hinton, Cambridge. Written and Produced for Acorn Computers Limited by Arch Technical Publications Limited, St. Lukes House, 5, Walsworth Road, Hitchin, Herts.

400,005

(i)

## CONTENTS (Cont'd)

| Paragrap | bh    |          |                              | Page |

|----------|-------|----------|------------------------------|------|

|          | 3.5   | VIA So   | ftware Instructions          | 18   |

|          |       | 3.5.1    | Data Input/Output            | 18   |

|          |       | 3.5.2    | Timer 1                      | 19   |

|          |       | 3.5.3    | Timer 2                      | 19   |

|          |       | 3.5.4    | Shift Register Operation     | 19   |

|          |       | 3.5.5    | Interrupt Operation          | 20   |

| 4.       | 6502A | CPU CO   | NNECTIONS                    | 20   |

|          | 4.1   | 6502A    | CPU Board to Acorn Bus (PL2) | 20   |

|          | 4.2   |          | CPU Board to I/O Unit (PL1)  | 21   |

| 5.       | PART  | S LIST   |                              | 21   |

|          | 5.1   | Mechai   | nical Parts                  | 21   |

|          | 5.2   | Electric | cal Parts                    | 21   |

## TABLES

| Table N | No.                           | Page |

|---------|-------------------------------|------|

| 1       | Data Buffer Enable Conditions | 10   |

| 2       | VIA Register Selection        | 12   |

| 3       | PCR Control Functions         | 12   |

| 4       | SR Control Functions          | 14   |

| 5       | Timer 1 Mode Selection        | 14   |

| 6       | Instruction Set Coding        | 16   |

| 7       | VIA Address Allocation        | 18   |

(ii)

FIGURES

| Figure I | No.                                    | Page |

|----------|----------------------------------------|------|

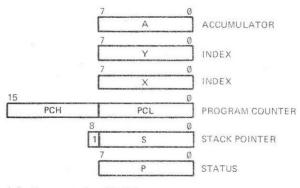

| 1        | CPU Board Block Diagram                | 1    |

| 2        | Microprocessor Internal Architecture   | 2    |

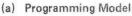

| 3        | Microprocessor Registers               | 3    |

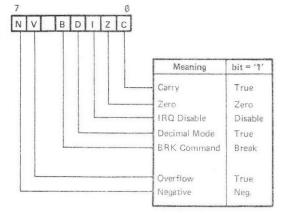

| 4        | Microprocessor Signal Timing           | 4    |

| 5        | DMA Timing (CPU Board Signals)         | 4    |

| 6        | RAM and VIA Select Circuit             | 5    |

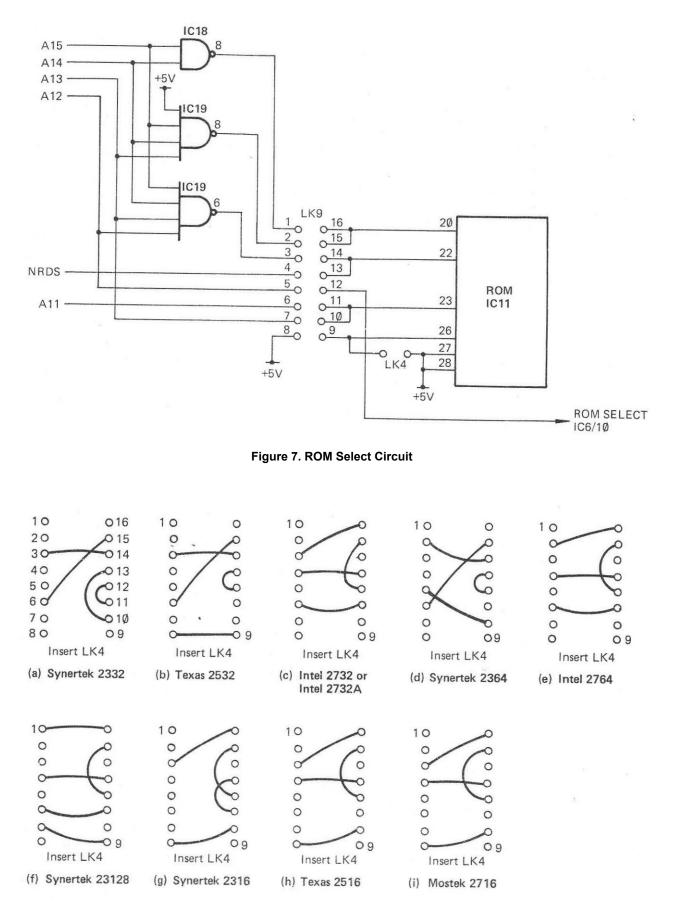

| 7        | ROM Select Circuit                     | 6    |

| 8        | LK9 and LK4 Configurations             | 6    |

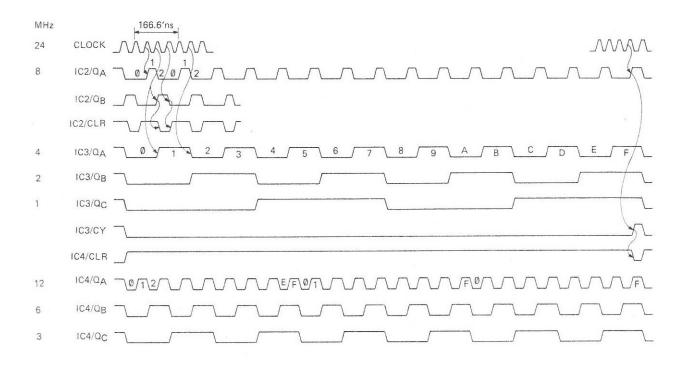

| 9        | System Clock Timing Diagram            | 8    |

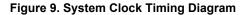

| 10       | Read/Write Control Circuit             | 9    |

| 11       | NRDS and NWDS Timing                   | 9    |

| 12       | Data Buffer Circuit                    | 9    |

| 13       | VIA Block Diagram                      | 10   |

| 14       | Typical VIA Operation Timing           | 11   |

| 15       | PCR Bit Significance                   | 12   |

| 16       | ACR Bit Significance                   | 13   |

| 17       | Typical Serial Data Transfer Operation | 13   |

| 18       | IFR Bit Significance                   | 14   |

| 19       | IER Bit Significance                   | 14   |

| 20       | 6502A CPU Memory Map                   | 18   |

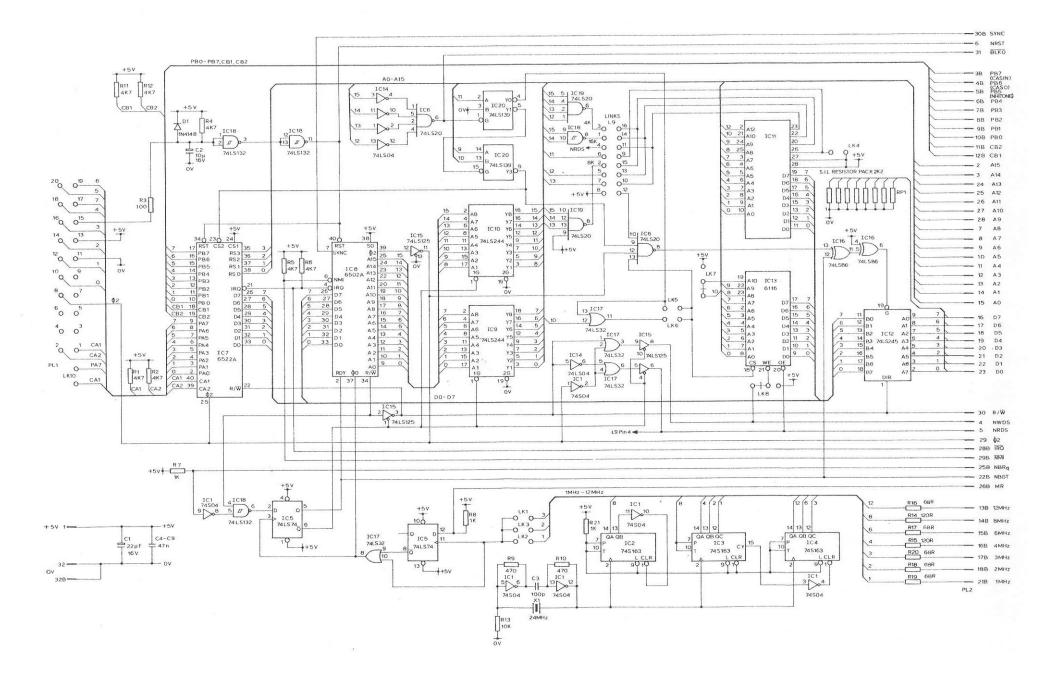

| 21       | 6502A CPU Board Circuit Diagram        | 23   |

(iii)

## 1. INTRODUCTION

#### 1.1 GENERAL

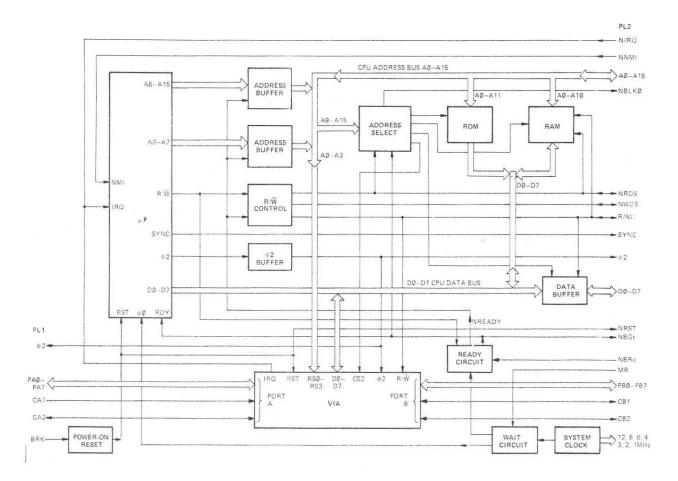

The 6502A CPU Board provides the Central Processor Unit (CPU) for a modular computer system. The CPU is constructed on a 100 x 160mm Eurocard which plugs into a standard Eurocard rack. A 6502A Microprocessor ( $\mu$ P) is run at 1, 2 or 3MHz from a 24MHz crystal controlled clock to provide the following CPU functions, refer also to the block diagram, Figure 1:

- Read Only Memory (ROM). A 28-pin DIL socket is provided for the installation of a ROM IC for the resident software. Links are wired on a header inserted in a 16-pin DIL socket to cater for a large range of 28-pin or 24-pin ROM ICs.

- Random Access Memory (RAM). A 24-pin DIL socket is provided for a 6116 2K x 8 bit static RAM IC. The RAM provides the stack and user memory areas. Other optional ICs such as 4118 may be used.

- Input/Output (I/O). A 6522A Versatile Interface Adaptor (VIA) IC fitted to the CPU Board provides two I/O Ports. The VIA Port (A) is

connected to PL1 to provide an interface with an external unit such as a Keyboard. The VIA Port ( B) is connected to PL2 to provide a User Port.

The CPU address, data and control lines are buffered for connection to the standard Acorn Bus via PL2. Additional interrupt and Direct Memory Access (DMA) lines are also connected to PL2, as are the System Clock outputs.

#### 1.2 LEADING PARTICULARS

#### 1.2.1 Mechanical

Construction : Single Eurocard printed circuit board.

Size : 100mm x 160mm

## 1.2.2 Power Supplies

+5V ± 5% at 520mA typically.

#### 1.2.3 Connections

Pin connections are given in Section 4.

1

400,005

Figure 2. 6502A Microprocessor Internal Architecture

400,005

2

Connectors

Double sided edge connector to Acorn Bus, TTL signal levels are used, DV to 0.4V = logic 0, >=+2. 4V logic 1.

20-way connector for external unit, i.e. Keyboard. TTL signal levels are used, 0V to 0.4V = logic0, => +2.4V = logic 1.

#### 2. CIRCUIT DESCRIPTION

The circuit diagram for the CPU Board is given on Figure 21 (filed at the end of this section) and should be referred to in conjunction with the description.

#### 2.1 MICROPROCESSOR

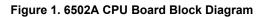

The 6502A Microprocessor ( $\mu$ P) IC8 operates at 1MHz, 2MHz or 3MHz, depending upon the setting of links LK1, LK2 and LK3. The microprocessor has a 16 bit address bus and an 8 bit bi-directional data bus. CPU control is provided by the Read/Write (R/W) and clock ( $\S$ 2) output signals, refer to block diagram, Figure 2. Two interrupt inputs are provided, Interrupt Request (NIRQ) and Non-Maskable Interrupt (NNMI). Power-on reset, ready and synchronization connections are also provided.

(b) P Register Bit Significance

400,005

The microprocessor address lines are buffered by IC9 and IC10. IC15 buffers the §2 and R/W lines.

#### 2.1.1 Microprocessor Registers

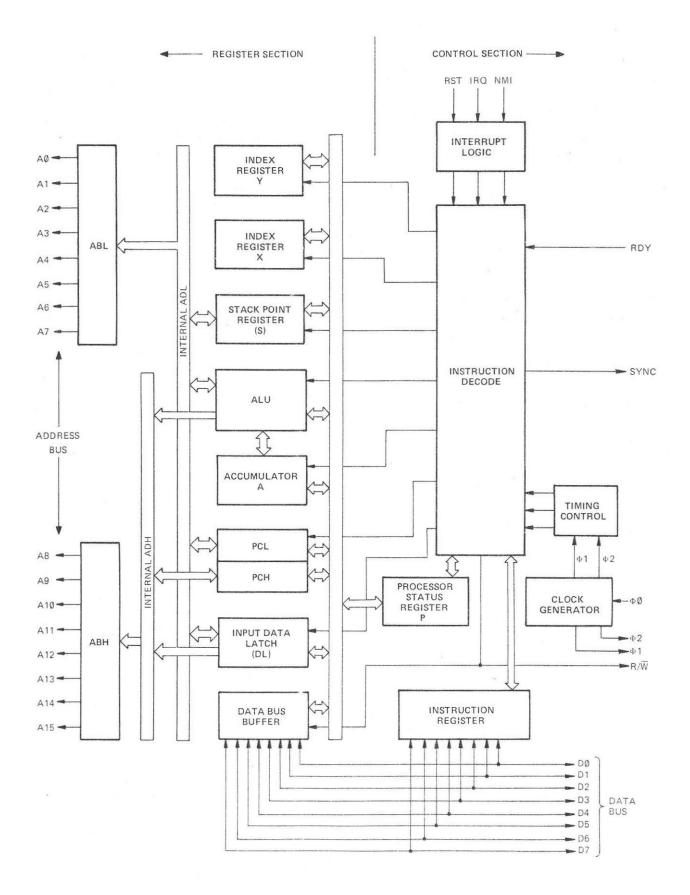

The 6502A Microprocessor internal registers are as shown on Figure 3. The functions of the registers are as follows:

- Accumulator (A). An 8 bit general purpose register used with the Arithmetic Logic Unit (ALU) for instruction execution. The A Register contents are not saved when an interrupt occurs.

- Index (X and Y). Two 8 bit index registers are provided. These registers are used for indexed addressing, a 16 bit offset can be used. The X and Y Register contents are not saved when an interrupt occurs.

- *Program Counter (PC).* A 16 hit register for the address of the instruction to be executed.

- Stack Pointer (S). A 9 bit register for the current stack address. On reset the S Register contains the address 01FF Hexadecimal (hex).

- Status (P), An 8 bit register that contains the microprocessor flags, refer to Figure 3. A '1' is loaded into the appropriate flag bit when a condition is true.

#### 2.1.2 Microprocessor Inputs and Outputs

The functions of the microprocessor inputs and outputs are as follows:

## ADDRESS LINES : A0-A15

These 16 lines are used to carry the address output from the microprocessor. The address lines are buffered onto the CPU Address Bus and the Acorn Bus by IC9 and IC10. The NREADY signal low from the Ready bistable IC5/6, enables IC9 and IC10, refer to para 2.5. When the NREADY signal is high, the outputs of IC9 and IC10 are disabled (high impedance) to allow external DMA control of the CPU Board Address Bus via the Acorn Bus.

#### DATA LINES : D0-D7

These 8 lines are used to carry the 8 bit data bytes to or from the CPU Data Bus. The CPU Data Bus is connected directly to the ROM IC11, the RAM IC13, the VIA IC7, and through the Data Buffer IC12, to the Acorn Bus.

#### READ/WRITE : R/W

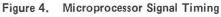

The R/W signal is used to identify the direction of data transfer on the data lines. The R/W signal is high for data transfer to the microprocessor and low for data output from the microprocessor. The timing of the R/W signal is given on Figure 4. The R/W signal is buffered to the Acorn Bus by IC15/3, refer to Read/ Write Control, para 2.6.

#### CLOCK INPUT : §0

The §0 clock input drives the microprocessor clock circuits at the frequency selected, refer to para 2.3.

CLOCK OUTPUT : §2 The §2 clock output is derived internally by the microprocessor from the §0 input. §2 is in phase with §0, refer to the timing diagram, Figure 4 (§1 is not used on the CPU Board). The §2 signal is buffered by IC15/11 to the CPU Board and the Acorn Bus.

#### SYNC

The SYNC signal is used to identify the microprocessor, instruction fetch cycles. The timing of the SYNC signal is shown on Figure 4. The SYNC signal may be used in conjunction with the RDY signal to induce a microprocessor halt state, see RDY below.

4

400,005

#### **READY SIGNAL : RDY**

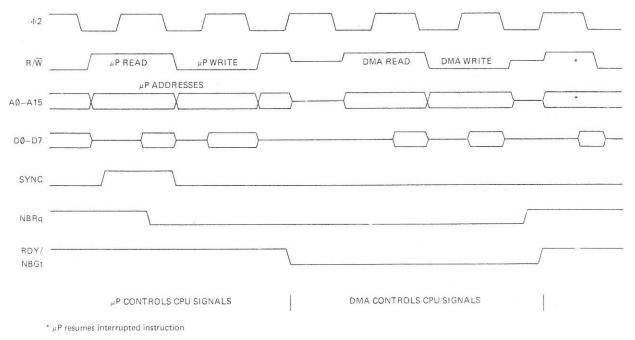

The RDY input signal to the microprocessor is normally high. When the microprocessor is used for DMA operations, a low input on the RDY line halts the microprocessor with the current address on the address lines, refer to para 2.5. If the microprocessor is executing a write cycle, the RDY signal is not set until the end of the cycle. Figure 5 shows a typical DMA operation with a halt state.

#### **INTERRUPTS : NIRQ, NNMI**

The microprocessor has two interrupt inputs, Interrupt Request (NIRQ) and Non-Maskable Interrupt (NNMI).

The NIRQ signal low is sampled at §2 time and if not masked by the interrupt mask flag, begin the interrupt sequence at the next microprocessor machine cycle, refer to para 3.3.1. The vectored addresses are loaded from memory locations FFFE and FFFF (hex).

The NNMI signal going low initiates an unconditional interrupt, which is otherwise similar to the NIRQ interrupt, refer to para 3.3.2. The vectored addresses in this case are loaded from memory locations FFFA and FFFB (hex).

## RESET : RST

The RST input is used to reset the microprocessor, or start the microprocessor from a power down condition. The NRST signal is held low on power-up for approximately 10ms, a positive edge then initiates a reset sequence, refer to para 3.3.3. An external reset can be initiated by applying 0V to PL1 pin 15, refer to para 2,11.

#### 2.2 ADDRESS SELECT

The Address Select circuits provide address line decoding in normal microprocessor and DMA operation, for the RAM and ROM fitted to the CPU Board, and also for the VIA. Links are used to change the signals applied to the ROM pins to cater for different ROM ICs, IC13 position may be used for an additional ROM IC, which is then selected by the RAM Select circuit.

## 2.2.1 RAM and VIA Selection

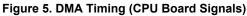

The RAM and VIA Select circuit is shown on Figure 6. IC20 is a dual two line decoder. IC20a is enabled by the Block 0 address, address lines A12—A15 all ' 0's (0 hex). The output from IC6/C is also connected to PL2 pin 31b to generate the NBLK0 signal low on the Acorn Bus.

Figure 6. RAM and VIA Select Circuit

Address line A11 low generates a low on the Y0 output IC20/4, to select the RAM IC13, either via LK5, or via OR gate IC17/11 and LK6. LK5 is inserted when 2K of RAM is required in Block 0, addresses 0000 to 07FF (hex). When only 1K of RAM is required, LK6 is inserted and the RAM is selected for addresses 0000 to 03FF (hex) by address line A10 low at the OR gate. A10 high inhibits the RAM selection for addresses 0400 to 07FF (hex). The RAM select signal from LK5 or LK6 also inhibits the I/O Data Buffer for microprocessor RAM operations, refer to para 2.9.

The Y1 output of IC20a enables IC20b. IC20b decodes A10 and A9, both lines '1', to produce a low on the Y3 output IC20/9 and select the VIA for addresses 0E00 to 0FFF (hex). IC20/9 low also inhibits the I/O Data Buffer when the VIA is selected for microprocessor operations, refer to para 2.9.

Two links LK7 and LK8 are provided on the CPU Board to permit the use of other RAM or ROM ICs in the IC13 socket. The track on the Board has to be cut and links soldered to use this facility. LK8 connects pin 21 to +5V instead of NWDS and LK9 connects pin 19 to +5V instead of A10.

When a 4118 RAM IC is used in IC13, LK7 is connected to +5V and LK6 link inserted to give addresses 0000 to 03FF (hex) for the RAM.

The IC13 position can be used for ROM ICs. In this case LK8 is connected to +5V and LK5 link inserted to give addresses 0000 to 07FF (hex) for the ROM. Suitable ICs are 2516 and 2716.

#### 2.2.2 ROM Selection

The ROM Select circuit is shown on Figure 7. The LK9 links are wired on a 16-pin DIL header that is inserted in the DIL socket. The link patterns for the various types of ROM IC which may be fitted in the IC11 socket, are shown on Figure 8. A link is also inserted in or removed from LK4 as indicated on Figure 8. The connection to LK9 pin 12 is used to inhibit the I/O Data Buffer during microprocessor memory read operations, refer to para 2.9.

The output of IC18/8 is low at LK9 pin 1 for all addresses in the range C000 to FFFF (hex) on the address lines.

The output of IC19/8 is low at LK9 pin 2 for all addresses in the range E000 to FFFF (hex) on the address lines.

The output of IC19/6 is low at LK9 pin 3 for all addresses in the range F000 to FFFF (hex) on the address lines.

The address lines A11 to A13 are connected to the appropriate pins on the ROM via links from LK9 pin 6, 5 and 7 respectively.

Signal NRDS is connected to the appropriate output enable (OE) pin on the ROM via a link from LK9 pin 4.

#### 2.3 SYSTEM CLOCK

The System Clock is driven by the 24MHz crystal oscillator circuit X1, IC1, C3, R9, R10 and R13. Synchronous binary counters IC2, IC3 and IC4 divide the 24MHz clock signal output of the oscillator to produce: 12, 8, 6, 4, 3, 2 and 1MHz clock signals. The clock signals are synchronized to the falling edge of the 1MHz signal, refer to Figure 9. The microprocessor clock frequency is selected by a link as follows:

| Link | Frequency |

|------|-----------|

| LK2  | 1MHz      |

| LK3  | 2MHz      |

| LK1  | 3MHz      |

The counter IC2 is configured to divide the 24MHz clock signal by three. The QB output is inverted by IC1 to clear IC2 every third clock pulse, refer to timing diagram, Figure 9. The IC2 QA output (8MHz) is connected to the enable P and T inputs of IC3, as well as to PL2 pin 14b via R15 (8MHz Acorn Bus clock).

The IC2 QA output is connected to the enable P and T inputs of counter IC3, so that IC3 counts every third 24MHz clock pulse. The QA, QB and QC outputs produce the 4, 2 and 1MHz clock signals. The 2 and 1MHz signals are connected to links LK2 and LK3 respectively, to provide the required microprocessor §0 clock input via the Wait Circuit, refer to para 2.4. The 4, 2 and 1MHz clock signals are output via R17, R19 and R20 onto the Acorn Bus via PL2 pins 16b, 18b and 19b respectively. The IC3 carry output is used to synchronize IC4.

The counter IC4 divides the 24MHz clock signal to produce 12, 6 and 3MHz outputs at QA, QB and QC. The 3MHz output is connected to link LK1 to provide the microprocessor §0 clock input if required. The 12, 6 and 3MHz clock signals are output via R14, R16 and R18 onto the Acorn Bus via PL2

pins 13b, 15b and 17b respectively. The carry output of IC3 is inverted by IC1 to clear IC4 every 2µs, thus ensuring that the IC4 outputs are synchronized to the 1MHz clock output from IC3, refer to timing diagram, Figure 9. Note that the IC3 carry output remains low, until the 8MHz clock signal at the enable T input goes high.

#### 2.4 WAIT CIRCUIT

The Wait Circuit provides the means for stopping the microprocessor for slow memory or peripheral operations. While the Memory Ready (MR) signal is high at PL2 pin 26b, the high on IC5/12 gives a low on the Q output pin IC5/8, so that the selected clock from link LK1, 2 or 3 is output from OR gate IC17/8. When signal MR goes low, the next positive going clock signal clears the Q output IC5/8 high to IC17/9. This applies a high on the microprocessor §0 input to stop the microprocessor. When MR goes high again IC5/8 is set low and the clock output to the microprocessor is enabled.

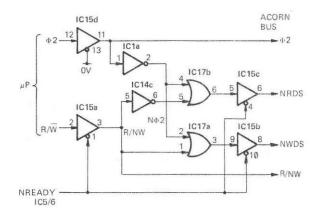

#### 2.5 READY CIRCUIT

The Ready Circuit is used to introduce a halt state in the microprocessor for DMA operations.

While the Bus Request signal NBRq on the Acorn Bus is high at PL2 pin 25b, or the pin is open circuit (R7 pulls-up IC1/9), IC18/5 low applies a high to IC5/2. The Q output IC5/5 sets the microprocessor RDY input high to allow normal operations. This signal is also output on the Acorn Bus as the Bus Grant signal NBGt at PL2 pin 22b. -

When NBRq goes low and the microprocessor R/W signal output is high (read), IC18/6 goes low, so that the next positive edge of the §0 clock from IC17/8 will reset IC5 Q output low. The low on the microprocessor RDY input induces a halt state, refer to Figure 5.

The Q output from IC5/6 inhibits the R/NW, NRDS and NWDS signals from buffers IC15 and the address line buffers IC9 and IC10, during the halt state, the buffer outputs go high impedance. When NBRq goes high the next positive edge of §0 sets the Q output IC5/5 high, to generate the RDY signal high and end the microprocessor halt state.

#### 2.6 READ/WRITE CONTROL

The Read/Write Control Circuit buffers the microprocessor R/NW output from IC8/34 and generates the NRDS and NWDS signals for the Acorn Bus. The circuit is shown on Figure 10.

Figure 10. Read/Write Control Circuit

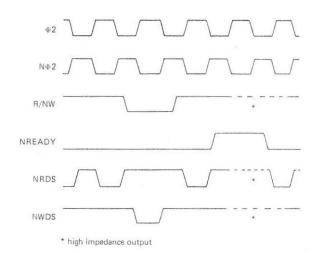

The §2 clock output from the microprocessor is buffered by IC15d and inverted by IC1a to enable IC17a and IC17b at each §2 clock time. The R/W signal output from the microprocessor is buffered by IC15a, then connected directly to IC17a and via inverter IC14c to IC17b. The Read and Write Control signals thus produced are buffered by IC15c and IC15b to generate the Read Strobe (NRDS) and Write Strobe (NWDS) signals for the Acorn Bus, refer to timing diagram, Figure 11. The IC5/6 Q output (N READY) high disables the buffers to the high impedance output state, to allow DMA control of the WNW, NR DS and NWDS Acorn Bus lines.

Figure 11. NRDS and NWDS Timing

## 2.7 READ ONLY MEMORY

The Read Only Memory (ROM) is selected by address lines A12—A15, refer to para 2.2.2. Various ROM ICs may be equipped in the IC11 position. IC13 may also be equipped with a ROM. When selected, address lines A0—A13 select the required location in the ROM, refer to para 2.2.2 and Figures 7 and 8 for

details of particular ROM address line connections. The data from the addressed location is output onto data lines D0—D7 by the NRDS signal low. When not selected the ROM data outputs are high impedance.

#### 2.8 RANDOM ACCESS MEMORY

The Random Access Memory (RAM) is selected by address lines A11--A15, refer to para 2.2.1. The CS input low selects the RAM. Signal NRDS low outputs the data from the location addressed by address lines A0—A10 onto data lines D0—D7. Signal NWDS low writes the data present on data lines D0—D7 into the location addressed by address lines A0—A10. When not selected the RAM data lines are high impedance.

#### 2.9 DATA BUFFER

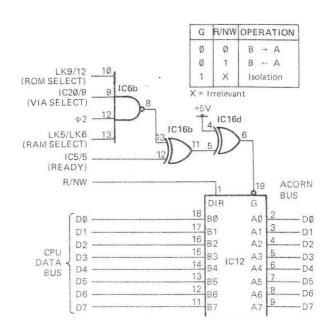

The Data Buffer Circuit controls the transfer of data between the CPU Data Bus and the Acorn Bus. The circuit consists of the bi-directional octal Bus Buffer IC12, exclusive OR gates IC16/6 and IC16/11, and NAND gate IC6/8, refer to Figure 12. The IC12 I/O lines are high impedance when the IC is not enabled.

For normal CPU operation the Bus Buffer is enabled for data transfers during the Phase 2 (§2) clock time, unless the ROM, RAM or VIA on the CPU Board is addressed, refer to Table 1 for truth table.

For DMA operation, the Bus Buffer is disabled for data transfers during the §2 clock time, when neither a ROM, nor a RAM address is present on the Acorn Bus address lines. The Bus Buffer is enabled by a ROM, or RAM address.

Figure 12. Data Buffer Circuit

400,005

| READ<br>Y | - | ELEC<br>DM RA |   | §2 | ان<br>13 | 16/<br>121 |   | IC12<br>G |

|-----------|---|---------------|---|----|----------|------------|---|-----------|

| 1         | 1 | 1             | 1 | 1  | 0        | 1          | 1 | 0         |

| 1         | Х | Х             | X | 0  | 1        | 1          | 0 | 1         |

| 1         | 0 | Х             | X | Х  | 1        | 1          | 0 | 1         |

| 1         | х | 0             | X | Х  | 1        | 1          | 2 | 1         |

| 1         | х | Х             | 0 | Х  | 1        | 1          | 0 | 1         |

| 0         | 1 | 1             | 1 | 1  | 0        | 0          | 0 | 1         |

| 0         | х | Х             | X | 0  | 1        | 0          | 1 | 0         |

| 0         | 0 | Х             | x | Х  | 1        | 0          | 1 | 0         |

| 0         | Х | 0             | X | Х  | 1        | 0          | 1 | 0         |

X = Irrelevant

## Table 1. Data Buffer Circuit Enable Conditions

When IC12 is enabled, the direction of data transfer is determined by the R/NW signal. R/NW high selects data transfer from the Acorn Bus (A input), to the CPU Data Bus (B output). R/NW low selects output from the CPU Data Bus (B input) to the Acorn Bus (A output). The Acorn Bus data lines D0—D7 are tied down to 0V by the Resistor Pack RP1.

## 2.10 VERSATILE INTERFACE ADAPTOR

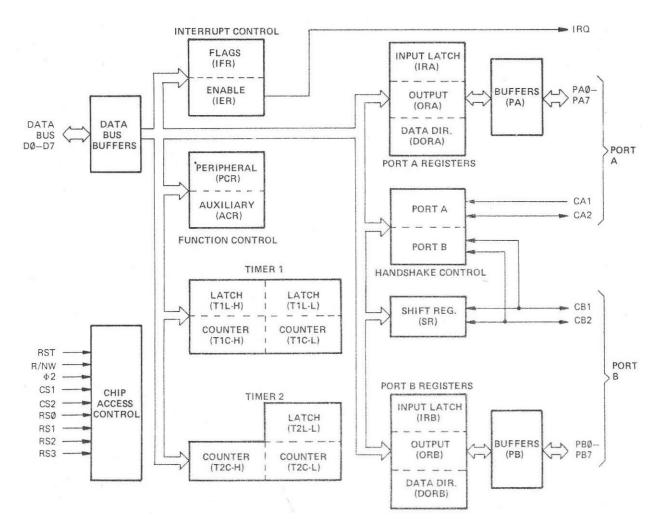

The Versatile Interface Adaptor (VIA) is used to provide two Input/Output (I/O) Ports for the CPU Board. Port A (PA0—PA7) is connected to PL1 for use with a Keyboard, Port B (PB0—PB7) is connected to PL2 to provide a general purpose I/O Port on the Acorn Bus. Handshaking capability is provided by the control lines CA1, CA2, CB1 and CB2. Refer to block diagram, Figure 13.

The VIA is selected by address lines A9 and A10 both high at IC20b, when the Y1 output from IC20a is low, this selection allocates addresses 0E00 to 0FFF (hex) to the VIA. The functions of the VIA are then selected by address lines A0—A3, which are connected to the register select inputs RS0—RS3. The VIA has the following internal registers:

- Two Output Registers (OR), one for each Port.

- Two Input Registers (I R), one for each Port.

- Two Data Direction Registers (DDR), one for each Port.

- A Peripheral Control Register (PCR).

Figure 13. VIA Block Diagram

10

400,005

Figure 14. Typical VIA Operation Timing

An Auxiliary Control Register (ACR). An Interrupt Flag Register (IFR). An Interrupt Enable Register (IER).

The address selection of the registers is given in Table 2.

| Hex | RS3 | RS2 | RS1 | RSØ | Register | Remarks                                |

|-----|-----|-----|-----|-----|----------|----------------------------------------|

| Ø   | Ø   | Ø   | Ø   | Ø   | ORB/IRB  | Controls hand-<br>shake Port B         |

| 1   | Ø   | Ø   | Ø   | 1   | ORA/IRA  | Controls hand-<br>shake Port A         |

| 2   | Ø   | Ø   | 1   | Ø   | DDRB     | Program Port B<br>I/O pins             |

| 3   | Ø   | Ø   | 1   | 1   | DDRA     | Program Port A<br>I/O pins             |

| 4   | Ø   | 1   | Ø   | Ø   | T1L-L    | Low order latch                        |

|     |     |     |     |     | T1C-L    | (Write)<br>Low order<br>counter (Read) |

| 5   | Ø   | 1   | Ø   | 1   | T1C-H    | Refer to para 2.10.6                   |

| 6   | Ø   | 1   | 1   | Ø   | T1L-L    |                                        |

| 7   | Ø   | 1   | 1   | 1   | T1L-H    |                                        |

| 8   | 1   | Ø   | Ø   | Ø   | T2L-L    | Low order latch                        |

|     | 2   |     |     |     | T2C-L    | (Write)<br>Low order<br>counter (Read) |

| 9   | 1   | Ø   | Ø   | 1   | T2C-H    | Refer to para 2.10.7                   |

| А   | 1   | Ø   | 1   | Ø   | SR       |                                        |

| В   | 1   | Ø   | 1   | 1   | ACR      |                                        |

| С   | 1   | 1   | Ø   | Ø   | PCR      |                                        |

| D   | 1   | 1   | Ø   | 1   | IFR      |                                        |

| E   | 1   | 1   | 1   | Ø   | IER      |                                        |

| F   | 1   | 1   | 1   | 1   | ORA      | No effect on<br>handshake              |

Table 2. VIA Register Selection

The VIA is also provided with two Timers T1 and T2, and an 8 bit Shift Register (SR). The Timers can be used to control the Port I/O lines to generate programmable-frequency square waves and/or to count externally generated pulses. The SR can be used to translate the 8 bit parallel data on D0—D7, to serial data on CB2 and vice versa,

The Reset (RST) input of the VIA is connected to the Power-on Reset Circuit. Signal NRST low clears all the internal registers to the '0' state, except T2 and SR. All I/O lines are set to input.

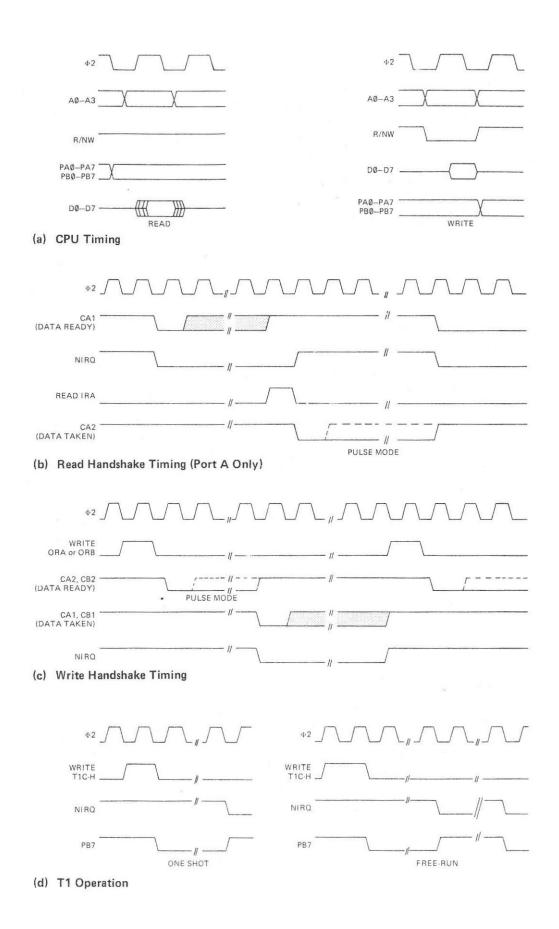

A timing diagram of some typical VIA operations is given on Figure 14. All timed operations are controlled by the 6502A CPU Board Phase 2 (§2) clock, except for serial data transfers when external clock mode is selected. A link (LK10) is provided to connect the PA7 line from PL1 to the CA1 input, when Keyboard input operation under interrupt control is required.

#### 2.10.1 Peripheral Control Register

The PCR is loaded by a microprocessor Write to the PCR address. The PCR is organized as shown on Figure 15. Table 3 gives the functions selected by PCR bits 1-3 for the Port A CA2 control line, the CA2 interrupt flag is IFR bit 0 (IFR0).

| D        | 7 | 6        | 5  | 4              | 3 | 2         | 1  | Ø              |

|----------|---|----------|----|----------------|---|-----------|----|----------------|

| FUNCTION | C | B2 Contr | 01 | CB1<br>Control | С | A2 Contro | 01 | CA1<br>Control |

## Figure 15. PCR Bit Significance

|   | R<br>2 | BIT<br>1 | FUNCTION                                                                                                                                                             |

|---|--------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ø | Ø      | Ø        | Input mode — Set CA2 interrupt flag<br>(IFRØ) on a negative transition of the<br>input signal. Clear IFRØ on a Read or<br>Write of the Port A output Register.       |

| Ø | Ø      | 1        | Independent Interrupt Input mode – Set<br>IFRØ on a negative transition of the CA2<br>input signal. Reading or writing ORA<br>does not clear the CA2 interrupt flag. |

| Ø | 1      | Ø        | Input mode – Set CA2 interrupt flag<br>on a positive transition of the CA2<br>input signal. Clear IFRØ with a Read<br>or Write of the Port A Output Register.        |

| Ø | 1      | 1        | Independent Interrupt Input mode – Set<br>IFRØ on a positive transition of the CA2<br>input signal. Reading or writing ORA<br>does not clear the CA2 Interrupt flag. |

| 1 | Ø      | Ø        | Handshake Output mode – Set CA2<br>output low on a Read or Write of the<br>Port A Output Register. Reset CA2<br>high with an active transition on CA1.               |

| 1 | Ø      | 1        | Pulse Output mode – CA2 goes low for<br>one cycle following a Read or Write of<br>the Port A Output Register.                                                        |

| 1 | 1      | Ø        | Manual Output mode The CA2 output is held low in this mode.                                                                                                          |

| 1 | 1      | 1        | Manual Output mode – The CA2 output<br>is held high in this mode.                                                                                                    |

**Table 3 PCR Control Functions**

#### 3.8 EXEC COMMAND

Any file created in the same way as Boot (para 3.7.2) can be executed by the DOS command EXEC. If you still have your Boot file on disc set Option to  $\emptyset$  (see para 3.7.1) and enter EXEC BOOT (from DOS) or (from BASIC) enter \*EXEC BOOT. The Boot file will now run with the same screen display as in para 3.7.2. The EXEC format is given in para 3.6.2.

#### 3.9 QUALIFIERS

In para 2.5 the CAT command display showed that qualifier "space" was currently being used, and that all files had a space to the left of the colon (:) indicating that all files were allocated the qualifier "space".

The qualifier facility is a useful aid to file handling. It is implemented by means of the SET and USE DOS commands.

The SET command sets the current qualifier to any character until either the BREAK key is pressed, or the SET command is again used. Pressing the BREAK key sets the current qualifier to "space". Files are saved with the current qualifier (except when a file is saved immediately after a USE command). Note that no space is allowed between SET and the character, e.g. SETA is acceptable while SET A is not.

The USE command allows the next file operation to use other than the current qualifier. After the next file operation the qualifier reverts to the current qualifier.

The most common use of qualifiers is to separate files according to their content, e.g. qualifier B for BASIC programs and qualifier D for data files.

There may be two (or more) separate files with the same file name providing they are in separate qualifiers. Hence with the Assembler you can have a source file called, say, UADEØ1 in qualifier "space" which you will assemble into an object file with the same name providing it has a different qualifier.

#### 3.10 SPOOLING

The SPOOL command will open a file for copying. To demonstrate you should enter:

SPOOL SPFILE

or if you are in BASIC:

**\*SPOOL SPFILE**

For demonstration purposes, to put something in the file named SPFILE you could EXEC BOOT, see para 3.8 (or \*EXEC BOOT if you are in BASIC).

To disable the SPOOL facility (closing the file) you must enter SHUT (or \*SHUT SPFILE from BASIC).

You will need a small BASIC program to read your SPFILE, so re-enter BASIC and key in this program:

10 D=FIN "SPFILE" 20 C=EXTD 30a IF C=PTRD GOTO b 40 A=BGET D 50 IF A=10 PRINT \$13 60 PRINT \$A 70 GOTO a 80b SHUT D 90 END

Line 20 uses the EXT command to determine the length of the file. Line 30 checks to see if the end of file has been reached before reading in a character from the file. Line 50 tidies up the screen format, adding a Return to each Line Feed. Saving this file with the file name "SPREAD" will allow you to use it again. By changing the file name in Line 10 you can read any file.

#### 3.11 DOS POINTER

When accessing files DOS maintains a pointer to the current access position within the file. The pointer can be read or changed by the BASIC PTR function. We used PTR in the SPREAD program (Line 30) in para 3.10 to exit from a loop when the end of file was reached. The pointer is set to "0" whenever a file is opened (FIN, FOUT' SPOOL, etc). We will look at the DOS Pointer again in para 6.1.

#### 3.12 DISC TITLES

We can give the disc in the current drive a title using the command TITLE followed by a space and the disc name we are allocating (in BASIC the command is preceded by a \*). Up to 13 characters may be used for a title.

#### 3.13 INFORMATION ON FILES

#### 3.13.1 INFO Command

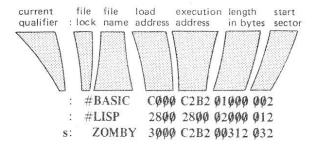

We can read information on any file in the current drive using the INFO command (followed by a space and the file name). The information displayed is in the following form:

#### 3.13.2 MON and NOMON Commands

The MON command turns on a message system which displays a file's information at each file access.

The NOMON command turns off the message system which was originally turned on by the MON command.

#### 3.14 MACHINE CODE PROGRAM EXECUTION

To execute a machine code program the GO command may be used (followed by a space and the execution address). We used this command in para 2.9.5 to reenter BASIC at C2B2 from DOS.

If the execution address is omitted the last known execution address will be used. Note that the current execution address is destroyed by CAT, and INFO does not set the execution address.

If a machine code program is on Drive Ø you can use the file name directly (as we called FORM4Ø and BASIC).

#### DOS COMMANDS AND ERROR MESSAGES

In the following commands, error and other messages, text, data and programs are said to be "displayed". They can, in fact be displayed on screen or printed or both, subject to the preceding Operating System control codes entered, see Table 1 in para 2.9.7.

File names and disc titles must be enclosed in quotes unless no spaces exist in file name. Only even numbers of quotes (or non at all) are allowed in file names or disc titles. Up to 13 characters are allowed in disc titles, and up to 7 characters are allowed in file names.

Legal drive numbers are dependent on the disc drive configuration, see para 2.6, but illegal drive numbers will simply cause the system to wait for the drive which is not there. Abbreviated command formats are shown following the full command formats.

#### 4.1 DOS COMMANDS

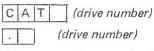

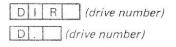

This command causes the Catalogue of drive (drive number), (or the current drive if (drive number) is omitted) to appear on the screen.

A typical Catalogue will look like:

\*CATØ Basic disc v1 drive Ø qual s opt Ø : #BASIC #LISP s: ZOMBY

The title of the disc is Basic disc v1; we are currently using drive  $\emptyset$  and qualifier s. The disc option is  $\emptyset$  (no auto-start features). Two files have been saved in qualifier "space", both of which have been locked to prevent careless deletion. One file has been saved in qualifier "s" and this has been left unlocked. The Catalogue is sorted alphabetically by qualifier and file name when it is output. The (*drive number*) can be omitted, or it must be  $\emptyset$ , 1, 2 or 3. If outside the range  $\emptyset$  to 3 then the message:

Drive ?

will be displayed.

If the *(drive number)* is specified, the default drive for subsequent commands is changed to that specified.

| D | E | L | Е | Т   | E     | (file name) |

|---|---|---|---|-----|-------|-------------|

| D | E |   |   | (fi | le na | ime)        |

This command deletes the *(file name)* in the current qualifier from the current disc's Catalogue. If the entire disc is Write Protected a

#### Disc prot

message is displayed. If the file is not found a

#### File ?

message is displayed. If the file is Locked a

File prot

message is displayed.

This command causes the Catalogue of the drive *(drive number)* to be loaded into memory at hex start

When 0V is applied to PL1 pin 15, C2 is rapidly discharged via R3. The NRST signal is set low until the 0V is removed and C2 has charged again. Similarly, C2 discharges via D1 when the +5V supply is switched off or interrupted.

## 3. SOFTWARE PARAMETERS

The following is a brief description of the software parameters affecting the CPU Board. Details are given of the 6502A Addressing Modes, Instruction Set and Interrupts, CPU memory addressing and the VIA software instructions.

#### 3.1 6502A ADDRESSING MODES

The 6502A Microprocessor is provided with the following 13 Addressing Modes:

#### ACCUMULATOR ADDRESSING

This form of addressing is represented with a one byte instruction, implying an operation on the accumulator.

#### IMMEDIATE ADDRESSING

In immediate addressing, the operand is contained in the second byte of the instruction, with no further memory addressing required.

#### ABSOLUTE ADDRESSING

In absolute addressing, the second byte of the instruction specifies the eight low order bits of the effective address while the third byte specifies the eight high order bits. Thus, the absolute addressing mode allows access to the entire 64K bytes of addressable memory.

#### ZERO PAGE ADDRESSING

The Zero Page instructions allow for shorter code and execution times by only fetching the second byte of the instruction and assuming a zero high address byte. Careful use of the Zero Page can result in significant increase in code efficiency.

# INDEXED ZERO PAGE ADDRESSING — (X, Y INDEXING)

This form of addressing is used in conjunction with the Index Register and is referred to as "Zero Page, X" or " Zero Page, Y". The effective address is calculated by adding the second byte to the contents of the Index Register. Since this is a form of "Zero Page" addressing, the content of the second byte references a location in page zero. Additionally due to the "Zero Page" addressing nature of this mode, no carry is added to the high order of 8 bits of memory and crossing of page boundaries does not occur.

#### INDEX ABSOLUTE ADDRESSING --- (X, Y INDEXING)

This form of addressing is used in conjunction with X and Y Index Register and is referred to as "Absolute, X" and "Absolute, Y". The effective address is formed by adding the contents of X or Y to the address contained in the second and third bytes of the instruction. This mode allows the Index Register to contain the index or count value and the instruction to contain the base address. This type of indexing allows any location referencing and the index to modify multiple fields resulting in reduced coding and execution time.

#### IMPLIED ADDRESSING

in the implied addressing mode, the address containing the operand is implicity stated in the operation code of the instruction.

#### RELATIVE ADDRESSING

Relative addressing is used only with branch instructions and establishes a destination for the conditional branch.

The second byte of the instruction becomes the operand which is an "Offset" added to the contents of the lower eight bits of the Program Counter when the counter is set at the next instruction. The range of the offset is -128 to +127 bytes from the next instruction.

#### INDEXED INDIRECT ADDRESSING

In indexed indirect addressing (referred to as [Indirect, X]), the second byte of the instruction is added to the contents of the X index Register, discarding the carry. The result of this addition points to a memory location on page zero whose contents is the lower order eight bits of the effective address. The next memory location in page zero contains the high order eight bits of the effective address. Both memory locations specifying the high and low order bytes of the effective address must be in page zero.

#### INDIRECT INDEXED ADDRESSING

In indirect indexed addressing (referred to as [Indirect, Y]). the second byte of the instruction points to a memory location in page zero. The contents of this memory location is added to the contents of the Y Index Register, the result being the low order eight bits of the effective address; The carry from this addition is added to the contents of the next page zero memory location, the result being the high order eight bits of the effective address.

#### ABSOLUTE INDIRECT

The second byte of the instruction contains the low order eight bits of a memory location. The high order eight bits of that memory location is contained in the

## INSTRUCTION SET

|          | INSTRUCTIONS                         | -    | AEDIA | ATE | AB  | SOLU | TE    | ZERO  | PAGE  | A    | ccui | M   | IM        | PLIED | T   | IND | X) | (1) | ND). 1 | T | Z PA | GE.X | T     | 85 1 |     | AB   | S. Y  | 1 8  | ELAT  | IVE | INC | IREC     | TT | 2 P  | AGE | . + | PROCESSOR S | TATUS     |                                         |

|----------|--------------------------------------|------|-------|-----|-----|------|-------|-------|-------|------|------|-----|-----------|-------|-----|-----|----|-----|--------|---|------|------|-------|------|-----|------|-------|------|-------|-----|-----|----------|----|------|-----|-----|-------------|-----------|-----------------------------------------|

| MNEMONIC | OPERATION                            | OP   | n     | #   | OP  | n    | # 0   | )P r  | #     | OP   | n    | #   |           | n 7   |     | P n | 1  | OP  | n      | # | OP   | #    | OP    | n    | #   | OP   | n #   | OF   | n     | #   | OP  | n .      | #  | OP   | -   | 4   | 7654        |           |                                         |

| ADC      | A + M + C - A (4) (1)                | 69   |       | -   | 6D  | 4    | 3 6   | 65 3  | -     | -    |      | "   | -         | -     | -+- | 1 6 | -  | 71  |        |   | 75   | 4 2  | -     |      |     |      | 4 3   | -    | +     | 1   |     | +        | -  | -    | +   | -+  | N V • B     |           |                                         |

| AND      | A ∧ M → A (1)                        | 29   |       |     | 2D  | 1    | 3     |       | 3 2   |      |      |     |           |       |     |     |    |     | 5      |   |      |      | 30    | 4    |     |      | 4 3   | - 11 |       |     |     |          |    |      |     |     | N           |           |                                         |

| ASL      | C-7 0-0                              |      |       |     | OE  | 6    | 3 1   | 06    | 5 2   | OA   | 2    | ,   |           |       |     |     |    |     |        |   | 16   | 6 2  | 1E    | 7    | 3   |      |       |      |       |     |     |          |    |      |     |     | N           | z c       | ASL                                     |

| BCC      | BRANCHONC = 0 (2)                    |      |       |     |     |      |       |       |       |      |      |     |           |       |     |     |    |     |        |   |      |      |       |      |     |      |       | 90   | 2     | 2   |     |          |    |      |     |     |             |           | BCC                                     |

| BCS      | BRANCHONC = 1 (2)                    |      |       |     |     |      |       |       |       | 1    |      |     |           |       | 1   |     |    |     |        |   |      |      |       |      |     |      |       | B    | 2 2   | 2   |     |          |    |      |     |     |             |           | BCS                                     |

| BEQ      | BRANCH ON 2 = 1 (2)                  |      |       |     |     |      |       |       |       | T    |      |     |           |       | 1   | 1   | 1  | 1   |        |   | 1    |      | 1     |      |     |      |       | FC   | 2     | 2   |     |          | 1  | 1    |     |     |             |           | BEQ                                     |

| BIT      | AAM                                  |      |       |     | 2C  | 4    | 3 2   | 24 3  | 2     |      |      |     |           |       |     |     |    |     |        |   |      |      |       |      |     |      |       |      |       |     |     |          |    |      |     |     | M M         | z .       | BIT                                     |

| BMI      | BRANCHONN = 1 (2)                    |      |       |     |     |      |       |       |       |      |      |     |           |       |     |     |    |     |        |   |      |      |       |      |     |      |       | 30   | 2     | 2   |     |          |    |      |     |     |             |           | BMI                                     |

| BNE      | BRANCH ON $Z = 0$ (2)                |      |       |     |     | Î    |       |       |       |      |      |     |           |       |     |     |    |     |        |   |      |      |       |      |     |      |       | DO   | 5 - 2 | 2   |     |          |    |      |     |     |             |           | BNE                                     |

| BPL      | BRANCH ON N = 0 (2)                  |      |       |     |     |      |       |       | 1     |      |      |     |           |       |     |     |    |     |        |   |      |      |       |      |     |      |       | 10   | 2     | 2   |     |          |    |      |     |     |             |           | BPL                                     |

| BRK      | BREAK                                | Π    |       |     |     |      | T     |       |       |      |      |     | 00        | 7     | 1   |     |    |     |        |   | 1    | 1    | 1     |      |     |      |       | T    | T     | 1   |     |          | 1  | 1    | T   | T   | 1           |           | BRK                                     |

| BVC      | BRANCH ON V = 0 (2)                  |      |       |     |     |      |       |       |       |      |      |     |           |       |     |     |    |     |        |   |      |      |       |      |     |      |       | 50   |       | 2   |     |          |    |      |     |     |             | • • •     | BVC                                     |

| BVS      | BRANCH ON V = 1 (2)                  |      |       |     |     |      |       |       |       |      |      |     |           |       |     |     |    |     |        |   |      |      |       |      |     |      |       | 70   | 2     | 2   |     |          |    |      | 1   |     |             |           | BVS                                     |

| CLC      | 0 → C                                |      |       |     |     |      |       |       |       |      |      |     | 18        |       | 1   |     |    |     |        |   |      |      |       |      |     |      |       |      |       |     |     |          |    |      |     |     |             | 0         | CLC                                     |

| CLD      | 0 - D                                |      |       |     |     |      |       |       |       |      |      |     | D8        | 2     | 1   |     |    |     |        |   |      |      |       |      |     |      |       |      |       |     |     |          |    |      |     |     |             | 0 • • •   | CLD                                     |

| CLI      | 0 I                                  |      |       |     |     |      |       |       |       |      |      |     | 58        | 2     | 1   |     |    |     |        |   |      |      |       |      |     |      |       |      |       |     |     |          |    |      | T   |     |             |           | CLI                                     |

| CLV      | 0 - V                                |      |       |     |     |      |       |       |       |      |      |     | B8        | 2     | 1   |     |    |     |        |   |      |      |       |      |     | 1    |       |      |       |     |     |          |    |      |     |     |             |           | 1                                       |

| CMP      | A - M                                |      |       |     |     |      |       | 25 3  | 1100  |      |      |     |           |       | C   | 1 6 | 2  | D1  | 5      | 2 | 05   | 4 2  | DD    | 4    | 3   | 09   | 4 3   |      |       |     |     |          |    |      |     |     | N           | z c       | CMP                                     |

| CPX      | X - M                                | 1    | - 1   | 2   |     |      |       | 4 3   | 1.000 |      |      |     |           | 1     |     |     |    |     |        | 1 |      |      | 1     |      |     |      |       |      |       |     |     |          |    |      |     |     | N           | z c       | 6                                       |

| CPY      | Y - M                                | Co   | 2     | 2   |     | 4    |       | 34 3  | -     | -    |      |     |           | _     | 1   | -   | -  | -   |        |   |      | -    | -     |      |     | -    | _     | +    | -     |     |     | _        |    | 1    |     |     | N           | z c       | CPY                                     |

| OE       | $M = 1 \rightarrow M$                |      |       |     | CE  | 6    | 3 0   | 6 5   | 2     | 2    |      |     |           |       |     |     |    |     |        |   | D6   | 6 2  | DE    | 7    | 3   |      |       |      |       |     |     |          |    |      |     |     | N           | z .       | DEC                                     |

| DEX      | X - 1 - X                            |      |       |     |     |      |       | 1     |       |      |      |     | CA        | ·     | 1   |     |    |     |        |   |      |      | 1     |      |     |      |       |      |       |     |     |          |    |      |     | - 1 | N · · ·     |           | 222611102200                            |

| DEY      | $Y = 1 \rightarrow Y$                |      |       |     |     |      |       |       |       |      |      |     | 88        | 2     | 1   |     |    |     |        |   |      |      |       |      |     |      |       |      |       |     |     |          |    |      |     | - 1 | N · · ·     |           | 1000 Co. 10                             |

| EOR      |                                      | 49   | 2     |     |     |      |       |       |       | 1.8  |      |     |           |       | 4   | 1 6 | 2  | 51  | 5      |   | 55   |      | 5D    |      |     | 59   | 4 3   |      |       |     |     |          |    |      |     |     | N · · ·     |           | 1                                       |

| INC      | M + 1 - M                            |      | -     | -   | EE  | 6    | 3 8   | 6 5   | 2     | -    |      | _   | -         |       | +   |     |    |     |        | - | F6 1 | 6 2  | FE    | 7    | 3   | -    | _     | -    |       |     |     |          | _  | -    | -   |     | N           |           | INC                                     |

| INX      | X + 1 - X                            |      |       |     |     |      |       |       |       |      |      | 1   | E.8       | ~ K   | 1   |     |    |     |        |   |      |      |       |      |     |      |       |      |       |     |     |          |    |      |     | - 1 | N · · ·     |           |                                         |

| INY      | Y + 1 → Y                            |      |       |     |     |      |       |       |       |      |      |     | C8        | 2     | 2   |     | 13 |     |        |   |      |      |       |      |     |      |       |      |       |     |     |          |    |      |     |     | N · · ·     |           | 1911/192 D                              |

| JMP      | JUMP TO NEW LOC                      |      |       |     |     | 3    |       |       |       |      |      |     | 1         |       |     | 1   |    |     |        |   |      |      |       |      |     |      | 1     |      |       |     | 6C  | 5        | 3  |      | 1   |     |             |           | JMP                                     |

| JSR      | JUMP SUB                             |      |       |     | 20  |      | 3     |       |       |      |      |     |           |       |     |     |    |     |        |   |      | Ĩ.   |       |      |     |      |       |      |       |     |     |          |    |      |     |     |             |           | JSR                                     |

| LDA      | M → A (1)                            | A9   | 2     |     | AD  |      | -     | 15 3  | +     | -    |      | -   |           | -     | A   | 1 6 | 2  | 81  | 5      | 2 | 85   | 4 2  | BD    | 4    |     | B9 - |       | -    | +     | -   |     | -        | -  |      | +   | -   | N · · ·     |           | LDA                                     |

| LDX      | M → X (1)                            | 1 1  |       |     | AE  |      |       | 46 3  |       |      |      |     |           |       |     |     |    |     |        |   |      |      |       |      | - 1 | BE   | 4 3   |      |       |     |     |          |    | Bó   | 4   | 2   | N · · ·     | 17.1      | 1000000                                 |

| LDY      |                                      | A0   | 2     |     |     |      |       | 44 3  |       |      |      |     | 1         |       |     |     |    |     |        |   | B4   |      | 80    |      | 3   |      |       |      |       |     |     |          |    |      |     |     | N · · ·     |           | 1948                                    |

| LSR      |                                      |      |       |     | 4E  | 6    | 3 4   | 16    | 2     | 44   | 2    | 1   | 1         |       |     |     |    |     |        |   | 56   | 6 2  | 5E    | 7    | 3   |      |       |      |       |     |     |          |    |      |     |     | 0           |           |                                         |

| OPA      | AVM-A                                |      |       |     |     |      |       |       |       |      |      |     | EA        | 2     | 1   |     |    |     |        |   |      |      |       |      |     |      |       |      |       |     |     |          |    |      |     |     | • • • •     |           | 0.0000000000000000000000000000000000000 |

| PHA      |                                      | 09   | 2     | 2   | OD  | 4    | 3 (   | 05 3  | 2     | +    | -    | -   | -+        |       | 0   | 1 6 | 2  | 11  | 5      | 2 | 15   | 4 2  | 10    | 4    | 3   | 19   | 4     | -    | -     | -   |     |          | +  |      | -   | -   | N · · ·     |           | -                                       |

| PHA      | A - Ms S - 1 → S<br>P - Ms S - 1 → S |      | 1     |     |     |      |       |       |       |      |      |     |           |       | 1   |     |    |     |        |   |      |      |       |      |     |      |       |      |       |     |     |          |    |      |     |     |             |           | РНА                                     |

| 10030000 | S + 1 → S MS → A                     |      |       |     |     |      |       |       | 1     | 1    |      |     | 08<br>68  |       | 1   |     |    |     |        |   |      |      |       |      |     |      |       |      |       |     |     |          |    |      |     |     |             |           |                                         |

| PLA      | S+1→S MS→A<br>S+1→S MS→P             |      |       |     |     |      |       |       | 1     |      |      |     |           |       | 1   |     |    |     |        |   |      |      |       |      |     |      |       |      |       |     |     |          |    |      |     |     | N · · ·     |           |                                         |

| ROL      | 4-[7 0]+-[C]+-                       |      | 1     |     | 2E  |      |       | 26 5  |       | 24   |      |     | 28        | 4     | 1   |     |    |     |        |   |      |      |       |      |     |      |       |      |       |     |     |          |    |      | 1   |     | REST        |           | PLP                                     |

| ROR      |                                      | ++   | -     |     |     | -    |       |       | -     | 6A   |      | 1   | +         | +     | +   | +   | +- | +   | ++     |   | -+-  |      | 3E    | 7    | 3   |      | +     | +    | +-    | -   |     | -+       | +  | -    | +   | -   | N · · ·     |           |                                         |

| RTI      |                                      |      |       |     | OL  | 0    | 2 6   | 10 5  | 12    | A    | -    |     | 40        | 6     | ,   |     |    |     |        |   | 76   | 0 2  | 7€    | 7    | 4   |      |       | 1    |       |     |     |          |    |      |     |     | N · · ·     |           |                                         |

| RTS      | RTRN SUB                             |      |       |     |     |      | 1     |       |       |      |      |     | 60        |       | ,   |     | 4  |     |        |   |      |      |       |      |     |      | 1     |      |       |     |     |          |    |      | 1   |     | (REST)      |           | R T I                                   |

| SBC      |                                      | E9   | 2     | 2   | ED  |      | 1     | -6    |       |      |      |     | 00        | 0     | 1   |     |    | F.  | 5      | 2 | EA   |      | ED    |      | 1,1 | FO   | 1.    |      |       |     |     |          |    |      |     |     | N V · ·     |           |                                         |

| SEC      | A - M - C - A (I)<br>1 - C           | 129  | -     | •   | 0   | 4    |       |       | 1     |      |      |     | 38        |       | 1   | 0   | 1  | 1   | 2      | ٢ |      | 1    | 10    |      | 2   |      | -   - | 1    |       |     |     | 1        |    |      |     |     | N V · ·     |           | Ne County of                            |

| SED      | 1-0                                  |      |       |     |     |      |       |       |       |      |      |     | -38<br>F8 | 2     |     |     | 1  |     |        |   |      |      |       |      |     |      |       |      |       |     |     |          |    |      |     |     |             |           | SEC SED                                 |

| SEI      | 1-0                                  | +    | -     | -   | -   | +    | +     |       | +-    | +-   |      |     | 78        |       |     | +   | +- | +   | +-+    | + | +    | +    | +     | +    |     |      |       | +    | +     | +   | +-+ |          | -  | +    | -   |     |             |           |                                         |

| STA      | A - M                                |      |       |     | 8D  | 4    | 3 4   | 35 3  | 1.    |      |      |     | 10        | -     |     | 1 6 | 10 | 91  | 6      | 2 | 95   |      | 90    | 6    |     | 99   | 5     |      |       | 1   |     |          |    |      |     |     |             |           | STA                                     |

| STX      | x - M                                |      |       |     | 8E  |      | 3 8   |       | 2     |      |      |     |           |       | 1   | 0   | 1  | 1   | 0      | - |      | - 1  | 190   |      | 0   | 33   | 1     |      |       |     |     |          |    | 96   | 4   | 2   |             |           | STX                                     |

| STY      | Y - M                                |      |       | - 1 | 80  | - 1  |       | 84 3  |       |      |      |     |           |       |     |     |    |     |        |   | 94   | 4 2  |       |      |     |      |       |      |       |     |     |          |    | ~    | -   | *   |             |           | STY                                     |

| TAX      | A X                                  |      |       |     |     |      |       |       | 1     |      |      |     | AA.       | 2     | 1   |     | 1  |     |        |   |      | 1    |       |      |     |      |       |      |       | 1.  |     |          |    |      |     |     | N · · ·     |           | TAX                                     |

| TAY      | A - Y                                |      | +     | -   |     | -    | +     | +     | +     | +    | -    | -   | AB        |       | ,   | +   | +  | +   | -      | - | +    |      | +-    | -    | -+  | +    | +     | +    | +     | +   |     | -+       | -  | -    | +   | -   | N · · ·     |           | TAY                                     |

| TSX      | 5 - x                                | 11   | 1     |     |     |      |       |       |       |      |      |     | BA        |       | 1   |     |    | 1   |        |   | -    |      | 1     |      |     |      |       |      |       | 1   |     |          |    |      |     |     | N · · ·     |           | TSX                                     |

| AXT      | A + X                                |      |       |     |     |      |       |       |       |      |      |     | AB        |       | 1   | 1   |    | 1   |        |   |      |      |       |      |     |      |       |      |       | 1   |     |          |    |      |     |     | N · · ·     |           | TXA                                     |

| TXS      | x → s                                |      |       |     |     |      |       |       |       |      |      |     | 94        |       | ,   |     |    |     |        |   |      |      |       |      |     |      |       |      |       |     |     |          |    |      |     |     |             |           | Txs                                     |

| TYA      | Y - A                                |      |       |     |     |      |       |       |       |      |      |     | 98        | 2     | 1   |     | 1  | 1   |        |   | -    |      |       |      |     |      |       |      |       |     |     |          |    |      |     |     | N · · ·     | •• z      | 100                                     |

|          | (1) ADD 1 to                         | NI   | FPA   | GE  | BOL | JND  | ARY   | IS CF | ROS   | SED  |      |     | -         |       |     | 1   | -  | 1   |        | × |      |      |       | L    |     |      |       |      | 1     | Å   |     | <u> </u> | 00 | -    |     |     |             |           |                                         |

|          | (2) ADD 1 TO                         | N    | IF B  | RAN | КСН | 000  | URS   | STO   | SAM   | E PA |      |     |           |       |     |     |    | 1   |        | × |      | DEX  |       |      |     |      |       |      |       |     | +   |          | DD | TRA  | CT  |     | M7<br>M6    | MEMORY    |                                         |

|          | ADD 2 TO<br>(3) CARRY N              |      |       |     |     | 000  | URS   | TO    | DIFF  | ERE  | NTP  | AGE |           |       |     |     |    | 1   |        | A |      |      | ULA   | IOR  |     |      |       |      |       |     | ٨   |          | ND |      | -   |     | n           | NO. CYC   |                                         |

|          |                                      |      |       |     | -   |      |       |       |       |      |      |     |           |       |     |     |    | 1   |        | M | ME   | MOR  | AY PE | RFF  | FEC | TIVE | 10    | DEC  | 22    |     | v   | 0        | R  |      |     |     | #           | NO. BYTE  |                                         |

|          | (4) IF IN DEC                        | IMA! | MC    | DF  | 7 F | LAG  | IS IN | IVA:  | ID .  |      |      |     |           |       |     |     |    | £   |        |   |      |      | RY PE |      |     |      |       |      | 10    |     | *   |          |    | LUSI |     |     | 77          | 140. 0110 |                                         |

Table 6. Instruction Set Coding

third byte of the instruction. The contents of the fully specified memory location is the low order byte of the effective address. The next memory location contains the high order byte of the effective address which is loaded into the sixteen bits of the Program Counter.

#### 3.2 6502A INSTRUCTION SET

The following Instruction Set is used by the 6502.A:

- ADC Add Memory to Accumulator with Carry

- AND "AND" Memory with Accumulator

- ASL Shift left One Bit (Memory or Accumulator)

- BCC Branch on Carry Clear

- BCS Branch on Carry Set

- BEQ Branch on Result Zero

- BIT Test Bits in Memory with Accumulator

- BMI Branch on Result Minus

- BNE Branch on Result Not Zero

- BPL Branch on Result Plus

- BRK Force Break

- BVC Branch on Overflow Clear

- BVS Branch on Overflow Set

- CLC Clear Carry Flag

- CLD Clear Decimal Mode

- CLI Clear Interrupt Disable Bit

- CLV Clear Overflow Flag

- CMP Compare Memory and Accumulator

- CPX Compare Memory and Index X CPY Compare Memory and Index Y

- DEC Decrement Memory by One

- DEX Decrement Index X by One

- DEY Decrement Index Y by One

- EOR "Exclusive or" Memory with Accumulator

- INC Increment Memory by One

- INX Increment Memory X by One

- INY Increment Memory Y by One

- JMP Jump to New Location

- JSR Jump to New Location Saving Return Address

- LDA Load Accumulator with Memory

- LDX Load Index X with Memory

- LDY Load Index Y with Memory

- LSR Shift One Bit Right (Memory or Accumulator)

- NOP No Operation

- ORA "OR" Memory with Accumulator

- PHA Push Accumulator on Stack

- PHP Push Processor Status on Stack

- PLA Pull Accumulator from Stack

- Pull Processor Status from Stack PLP

- ROL Rotate One Bit Left (Memory or Accumulator)

- ROR Rotate One Bit Right (Memory or Accumulator)

- RTI Return from Interrupt

- RTS Return from Subroutine

- SBC Subtract Memory from Accumulator with Borrow

- Set Carry Flag SFC

- Set Decimal Mode SFD

- SEI Set Interrupt Disable Status

- STA Store Accumulator in Memory Store Index X in Memory

- STX Store index Y in Memory STY

- TAX Transfer Accumulator to Index X

- Transfer Accumulator to Index Y TAY

- TSX Transfer Stack Pointer to Index X

- TXA Transfer Index X to Accumulator

- TXS

- Transfer Index X to Stack Register

- TYA Transfer Index Y to Accumulator

The coding, number of cycle and number of bytes for each address mode, together with the status codes are given on Table 6.

#### 6502A INTERRUPTS AND RESET 3.3

The 6502A microprocessor has two interrupt signal inputs NIRQ and NNMI and a reset input NRST. These inputs are used to load vectored addresses into the PC. The instructions located at the addresses are the first instructions of the relevant interrupt or start routine.

#### 3.3.1 Interrupt Request

A low level on the NIRQ input will initiate an interrupt sequence at the end of the current instruction, provided that the interrupt mask bit (I) in the Processor Status Register (P) is '0'. The contents of the Program Counter (PC) and the P Register are stored in the stack. The I bit is then set to '1' in the P Register. At the end of this cycle the PCL byte is loaded from address FFFE (hex) and the PCH byte is loaded from address FFFF (hex), transferring program control to the memory vector located at these addresses.

#### 3.3.2 Non-Maskable Interrupt

A negative going edge on the NNMI input will initiate an interrupt sequence at the end of the current instruction, the P Register I bit has no effect. The sequence is as described for NIRQ, except that PC is loaded from addresses FFFA (hex) and FFFB (hex).

#### 3.3.3 Reset

The NRST input low inihibits microprocessor operation. When a positive edge is detected the microprocessor starts the reset sequence. After the system initialization time of six clock cycles, the P Register I bit is set to a '1'. The PC is loaded from addresses

FFFC (hex) and FFFD (hex), transferring program control to the memory vector located at these addresses.

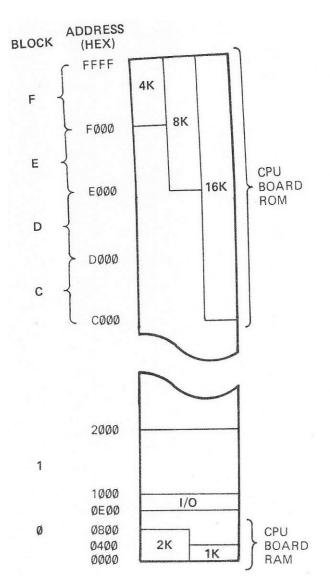

#### 3.4 CPU MEMORY ADDRESSING

The CPU RAM and ROM are assigned to the addresses shown in the Acorn Memory Map, Figure 20. The different types of ROM are selected by means of the links fitted to the DIL header that is inserted in LK9, refer to pare 2.2.2. The 1K or 2K RAM option 1 is selected by LK5 and LK6, refer to Para 2.2. IC13 may also be used for a ROM IC instead of a RAM IC.

Figure 20. 5502A CPU Memory Map

#### 3.5 VIA SOFTWARE INSTRUCTIONS

The operation of the VIA is controlled by program instructions from the microprocessor. The VIA is

assigned addresses 0E20 to 0E2F (hex), although because of incomplete decoding on the CPU Board, the address block 0E00 to 0FFF (hex) can only be used for the VIA, The VIA Register addressing is given on Table 7. The two Ports of the VIA are designated Port A and Port B.

| ADDR | ESSE | BITS | R/N | IW F | EGISTER                         | FUNCTION                                                                                                       |

|------|------|------|-----|------|---------------------------------|----------------------------------------------------------------------------------------------------------------|

| Ø    |      | Ø    |     | 2    | RB<br>ORB<br>IRA<br>ORA<br>DDRB | Input Register B<br>Output Register B<br>Input Register A<br>Output Register A<br>Data Direction<br>Register B |

| Ø    | Ø    | 1    | 1   | -    | DDRA                            | Data Direction<br>Register A                                                                                   |

| ø    | 1    | Ø    | ø   | 1    | T1C-L                           | T1 Low Order<br>Counter                                                                                        |

| ø    | 1    | Ø    | ø   | Ø    | T1L-L                           | T1 Low Order Latch                                                                                             |

| Ø    | 1    | Ø    | 1   | -    | T1C-H                           | T1 High Order<br>Counter                                                                                       |

| ø    | 1    | 1    | Ø   | -    | T1L-L                           | T1 Low Order Latc                                                                                              |

| Ø    | 1    | 1    | 1   | -    | T1L-H                           | T1 High Order Latc                                                                                             |

| 1    | Ø    | Ø    | Ø   | 1    | T2C-L                           | T2 Low Order<br>Counter                                                                                        |

| 1    | Ø    | Ø    | Ø   | Ø    | T2L-L                           | T2 Low Order Late                                                                                              |

| 1    | Ø    | ø    | 1   | -    | T2C-H                           | T2 High Order<br>Counter                                                                                       |

| 1    | Ø    | 1    | Ø   | -    | SR                              | Shift Register                                                                                                 |

| 1    | Ø    | 1    | 1   | -    | ACR                             | Auxiliary Control<br>Register                                                                                  |

| 1    | 1    | Ø    | Ø   | -    | PCR                             | Peripheral Control<br>Register                                                                                 |

| 1    | 1    | Ø    | 1   | -    | IFR                             | Interrupt Flag<br>Register                                                                                     |

| 1    | 1    | 1    | Ø   | -    | IER                             | Interrupt Enable<br>Register                                                                                   |

| 1    | 1    | 1    | 1   | 1    | IRA                             | Input Register A<br>(no handshaking)                                                                           |

| 1    | 1    | 1    | 1   | Ø    | ORA                             | Output Register A<br>(no handshaking)                                                                          |

Table 7. VIA Address Allocation

#### 3.5.1 Data Input/Output

The selection of the input/output pins of both Ports is controlled by the Data Direction Registers (DDRA, DDRB). A pin is selected for input or output by the corresponding bit in the DDR, input is selected by a '0' hit, output by a '1' bit.

The data bits to be output from a Port are loaded into the corresponding Output Register (ORA, ORB). The bits are set onto the Port output lines at the end of the Write instruction. Writing to a pin selected for input loads the Output Register bit, but. has no effect on the output pin. The Input Registers (IRA, IRB) are loaded by the corresponding CA1 or CB1 signal, when input latching is enabled by the control bit in the ACR. A microprocessor Read operation then reads the contents of the IR. When input latching is disabled, a Read operation reads the current state of the Port input pin.

"Handshaking" is available on Port A for both input and output, but only for output on Port B. Handshaking signals are controlled automatically by Reading or Writing to Port A or Port B Registers, RS0—RS3 = 0 or 1 (hex). When Writing or Reading to Port A Registers with RS0—RS3 = F (hex), handshaking is disabled.

The handshaking signal operation is defined by the appropriate bits of the PCR, refer to para 2.10.1.

#### 3.5.2 Timer 1

Timer 1 is controlled by the ACR, refer to para 2.10.2. For a single timed interrupt operation, Timer 1 is set by loading the Low Order Latch T1L-L and then the High Order Counter T1C-H. The contents of T1L-L are loaded into Counter T1C-L by the action of loading T1C-H. T1 is counted down to zero by the §2 clock. When zero is reached the interrupt flag IFR6 is set and, if interrupt enable IER6 is a '1', signal NIRQ is set low. IFR6 is reset by writing to T1C-H, or reading T1C-L.

For continuous interrupt (free-run) operation the Latch T1L-H has to be loaded as well as the Counter T1C-H. When T1 counts down to zero in this mode, T1C-L and T1C-H are reloaded from T1L-L and T1L-H, to restart the count down cycle.

When the PB7 output pin is selected for a single pulse operation, T1 operates as described above. A negative pulse is generated on PB7 for the duration of the timed interrupt. The pulse length = (n + 1.5) §2, where n is the number loaded in the Counter. The DDRB bit 7 must be 1 for PB7 to function as an output.

For a square wave output on PB7, T1 operates in the free-run mode as described above. PB7 is low for (n + 1.5) §2 and high for (n + 2) §2.

The T1 Latches may be loaded with a different number, while the Counters are counting down. When in the free-run mode, the new value is loaded into the Counters, when the count down reaches zero. If PB7 output is selected the output can thus be a complex waveform.

#### 3.5.3 Timer 2

Timer 2 is controlled by the ACR, refer to para 2.10.2.

The T2 single timed interrupt operation is similar to that described for T1. The T2 interrupt flag is IFR5 and the interrupt enable IER5, After the count down the Counters roll over to all '1's and continue counting. The Counters can be read to determine how long the interrupt has been set. Reading T2C-L resets the interrupt flag IFR5. Writing to T2C-H also clears IFR5. T2 does not have a High Order Latch.

The T2 Low Order Latch T2L-L is also used to control Shift Register operations in the following modes:

- Shift in under T2 control.

- Free-running output at rate determined by T2.

- Shift out under T2 control.

For further details, refer to Shift Register Operation para 3.5.4.

In the pulse counting mode T2 is counted down from a number (loaded into the Counters as described above) by negative going pulses on input PB6. The DDRB bit 6 must be set to '0' to select input. When T2 = '0' IFR5 is set and, if IER5 is a '1', signal NIRQ is set low. Writing to T2C-H clears IFR5.

#### 3.5.4 Shift Register Operation